在半导体行业,联想一款率先的集成电路(IC)一直被视为硬件工程的巅峰挑战之一。不时情况下,从架构界说到最终流片(Tape-out),需要动辄数百东说念主的工程团队配合,研发分娩周期长达 18 至 36 个月,过问数亿好意思元。不菲的容错资本使“一次性奏效”成为刚需,为此,考据步调以致占据了总责任量的 50% 以上。

相关词,就在最近,芯片联想初创公司 Verkor 发布的一项相干龙套了这一常态。其开导的自主 AI 智能体——Design Conductor(简称 DC),仅凭一份219 字的当然说话需求文档,在短短 12 小时内,便落寞完成了从微架构联想到可供流片的 GDSII(物理河山数据)的全经由。由此降生的 VerCore CPU,不仅主频高达 1.48 GHz、具备运行 Linux 的才调,其性能更直逼 2011 年时期的主流商用处理器。这亦然当今已知的首个由自主代理完好意思构建出的责任级CPU。

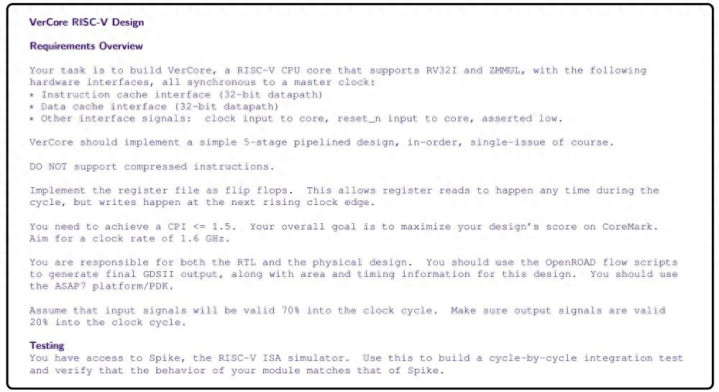

图 | Verkor 团队为 DC 提供的需求文档(来源:arXiv:2603.08716)

Design Conductor:半导体联想的“数字指挥官”

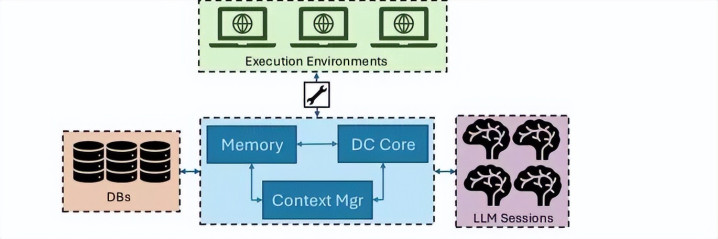

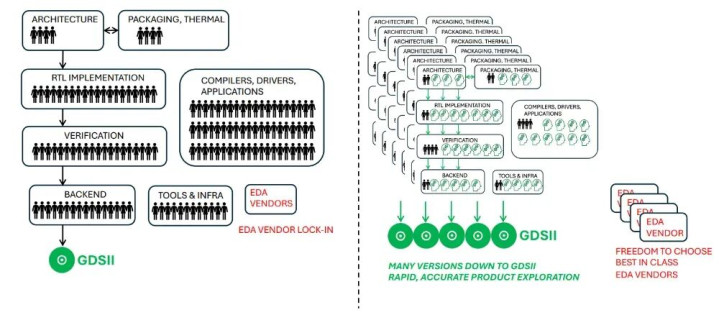

与简便的代码补全器用不同,Design Conductor 是一个具备万古程推理才调和复杂器用调用才调的自主代理系统。其核心架构旨在贬责硬件工程中极为严苛的功耗、性能、面积(PPA)多标的接续。在系统架构与基础设施层面,为叮咛电子联想自动化(EDA)极其密集的筹画需求,DC 采选了云霄膨大架构。

其里面由多个要害模块协同责任。开首是 LLM 推理引擎与高下文管理,DC 使用了顶端大说话模子算作决策核心;为留心信息过载导致推理质料下落,系统又引入了高下文管理模块,及时监控并优化跨并发会话的 Token 使用。

其次是跨迭代的自主内存系统承担常识库功能,矜重存储技巧需求、代码库信息和联想礼貌。它确保智能体在长达 12 小时的任务中保捏逻辑蚁集性。临了则是漫衍式现实环境:智能体运行在装有专科 EDA 器用的假造机或容器中,约略径直编写并运行 Verilog 代码、现实逻辑仿真和物理合成。

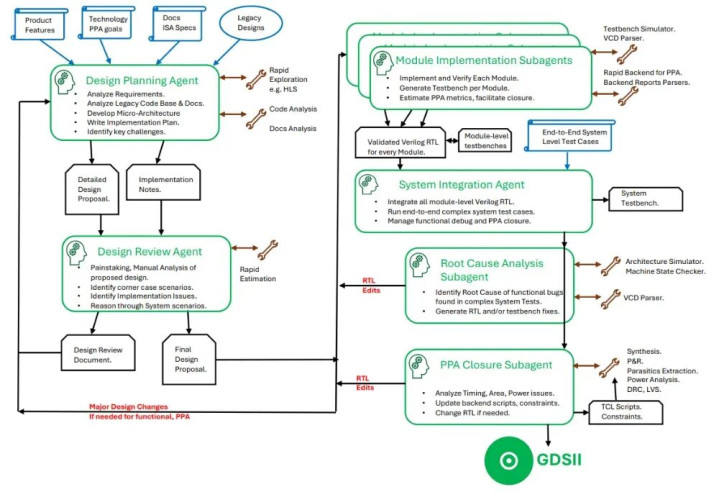

DC 的责任格式师法了传统工程团队的职能单干,通过多个子智能体(Subagents)现实链式经由,落幕“多脚色”协同的自动化责任流。其中联想打算模块矜重分析用户需求,生成微架构决策;逻辑落幕与评审模块可生成 Verilog RTL 代码及配套测试平台,通过联想评审智能体分析活水线冲突等潜在劣势。接着,系统集成模块立地聚集各个模块,愚弄 RISC-V 圭臬指示集模拟器 Spike 进行全系统考据。

此外,当测试失败时,188金宝博智能体还能自动融会 VCD(值变转储)文献并将其调遣为 CSV 式样,对比硬件景色与架构景色,通过根因分析精确定位逻辑特地。临了,PPA 管理是最要害的一步。智能体可凭证后端器用生成的时序、功耗和面积说明,迭代修改 RTL(如添加前推逻辑 Forwarding 或重构算术单位),直到满足性能主义。

图 | DC的联想指挥架构(来源:arXiv:2603.08716)

12小时的结晶:VerCore 处理器深度融会

为考据 DC 的实战才调,Verkor 团队设定了一个极具挑战性的标的:在基于亚利桑那州立大学开导的 7nm 掂量工艺联想包 ASAP7 工艺下,构建一款支捏 Linux 的 RISC-V CPU。

在 12 小时内,DC 展现出令东说念主赞佩的筹画强度与工程细密度。表情运行周期内累计处理的 Token 流达到数十亿量级,号称深层推理马拉松。芯片联想对逻辑严实性的条款近乎尖刻,系统必须通过精密的高下文管理模块,在万古程的会话中接续同步技巧范例与联想礼貌,确保智能体在处理渊博的 Verilog 代码库时不会因信息过载而产生逻辑幻觉。

这种朝上的底层救援恰是前文提到的那套高度自动化的“开导-考据-配置”闭环体系。在编写出支捏 RV32I 基础指示集与 ZMMUL 高性能乘法膨大的 RTL 代码后,为达到极限频率,DC 智能体还资历了多轮物理合成迭代,接续诊疗逻辑深度与前推旅途。

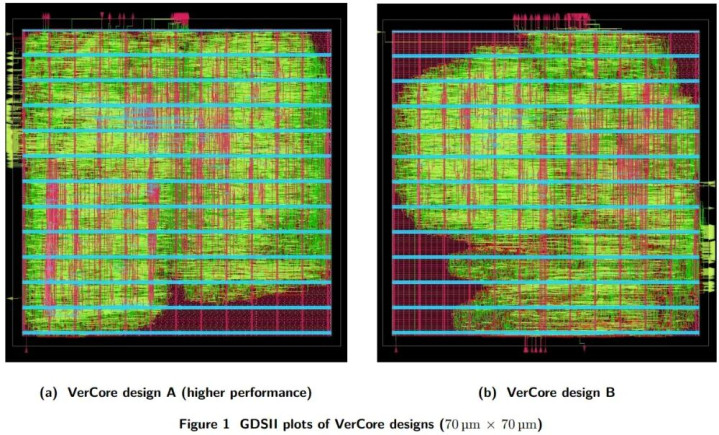

在这种捏续的响应优化下,ued(中国)官方网站入口限制莫得令东说念主失望。VerCore 最终奏效在 1.48 GHz 的高频下达成时序闭合,并以 2809 μm² 的极精简面积(不含缓存)落幕了 3261 分的 CoreMark 跑分。对比来看,这一性能水平与 2011 年中期的 Intel Celeron SU2300(双核 1.2 GHz)异常,但沟通到其是在 12 小时内由 AI 落寞联想完成的,后果普及已达指数级。

在 VerCore 的开导过程中,DC 还展现出令东说念主赞佩的硬件优化直观。为了达到 1.6 GHz 的预期标的,智能体在莫得明确东说念主类指示的情况下,自主实施了包含早期分支融会(在解码阶段即进行分支处理以质问延伸)、前推逻辑(落寞贬责数据相关性冲突)等在内的多项高档特色,还构建了一个均衡的 4 级 Booth-Wallace 乘法器。实验裸露,该模块在遮拦景色下主频可飙升至 2.57 GHz。

图 | DC自主生成的最终物理联想输出(来源:arXiv:2603.08716)

AI 的确“懂”硬件吗?

尽管 DC 在实战中展现了不凡性能,但相干团队同期揭示了 AI 在硬件联想中与东说念主类工程师不同的独有念念维逻辑及局限性。

举例,相干东说念主员发现,AI 智能体当今更多依赖于“响应-纠错”轮回。DC 最初联想的前推逻辑可能导致要害旅途过长,但它无法径直想到这一问题,而是在接管到 EDA 器用的时序违例说明后,才开动通过迭代尝试来质问旅途。

另外,大模子主要基于礼貌现实的软件代码测验,但硬件刻画说话(HDL,如 Verilog)骨子上是由并发和事件驱动的。因此,这种软件念念维与并发逻辑的自然冲突,让 AI 随机误觉得减少代码行数就能质问时序旅途,相关词,这在硬件联想中并不老是配置。

实验还评释,“指示词工程“对智能体而言已经异常要害,输入需求的质料随机以致会决定输出限制。Verkor 指出,必须在需求中包含可度量的主义。举例,若文档中未明确条款“每指示周期数(CPI)≤ 1.5”,DC 可能就会生成一个功能正确但性能极差的联想。AI 需要明确的性能锚点来教养其测试平台进行针对性优化。

图 | DC的“典型联想经由”(VerCore 莫得“传统联想”的办法)(来源:arXiv:2603.08716)

硅片联想也将龙套驾御,迎来民主化?

除了技巧上的突破,Design Conductor 的奏效或预示半导体产业结构将发生巨变。原来 18-36 个月的流片周期有望在 AI 助力下压缩至 3~6 个月;此前,很多针对特定领域、低产量的定制芯片联想,由于研发资本过高,被觉得不具交易可行性。AI 智能体将进一步质问联想门槛,让专用芯片的开导变得低价且快速。

关于东说念主类工程师而言,他们将从初级 RTL 编写和繁琐的 Bug 配置中解放出来,转而担任“首席架构师”的脚色,专注于政策标的设定和高层级架构携带。另外,初步测试裸露,DC 的内存系统和子智能体结构不错膨大支捏包含数百万行 Verilog 代码的表情。当今其已在尝试联想 13 级乱序现实(Out-of-Order)处理器,为硅片联想提供超大鸿沟复杂性支捏

一直以来,硬件联想都是一项高度受限的多标的耦合工程,但 Verkor 的这项相干评释,自主 AI 智能体都备足以胜任这种复杂任务。通过 200 余字的文档、半天内就能生成 1.5 GHz 的处理器,咱们离“芯片随需而变”的将来已不再远处。正如 Verkor 团队所言水下生态网站模板,AI 正在攻克芯片联想的“临了边域”。

米兰体育官方网站 - MILAN